Overcoming the Measurement Challenges of Advanced Semiconductor Technologies

DC, Pulse, and RF-From Modeling to Manufacturing

# Overcoming the Measurement Challenges of Advanced Semiconductor Technologies

DC, Pulse, and RF-From Modeling to Manufacturing

1st Edition

#### **Foreword**

The editors would like to thank the Keithley employees and customers who contributed articles for the first edition of this reference work. Their contributions provided invaluable insights on the latest semiconductor technologies and the measurement solutions now emerging to address them.

Keithley contributors to the First Edition include:

Pete Hulbert, Industry Consultant

Jeff Kuo, Sr. Applications Engineer

David Rose, Sr. Staff Engineer

David Rubin, Sr. Industry Market Manager

Carl Scharrer, Principal Industry Consultant

Lee Stauffer, Lead Industry Consultant

Steve Weinzierl, Applications Engineering Manager

Yuegang Zhao, Lead Applications Engineer

# **Table of Contents**

| I   | Introduction                                                                                                                                     |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|

|     | Meeting the measurement challenges of the 65nm node                                                                                              |

| II  | Advanced Transistor Gates and Thin Oxides                                                                                                        |

|     | Integrating high frequency capacitance measurement for monitoring process variation of equivalent oxide thickness of ultra-thin gate dielectrics |

|     | Qualifying high $\kappa$ gate materials with charge-trapping measurements                                                                        |

|     | How to get accurate trap density measurements using charge pumping                                                                               |

| III | RF Modeling and Process Control of<br>High Performance Analog and BiCMOS Devices                                                                 |

|     | RF wafer testing: an acute need, and now practical                                                                                               |

|     | Statistical process control of wireless device manufacturing requires production worthy s-parameter measurements 47                              |

| IV  | Reliability Testing                                                                                                                              |

|     | Wafer level reliability testing—a critical device and process development step                                                                   |

|     | Making charge-pumping measurements with the Model 4200-SCS Semiconductor Characterization System                                                 |

|     | High throughput gate dielectric reliability testing:  Digging out from the backlog                                                               |

|     | Improved thermal stability of copper vias using a cyclical stress test 82                                                                        |

|     | Reducing parametric test costs with faster, smarter parallel test techniques                                                                     |

| V   | Femtoamp DC Leakage for Mobile ICs                                                                                                               |

|     | Tips, tricks, and traps for advanced SMU DC measurements 100                                                                                     |

|     | Parametric test hardware for ultra-low current measurements111                                                                                   |

| VI  | Appendix A: Selector Guides121                                                                                                                   |

| VII | Appendix B: Glossary133                                                                                                                          |

# OVERCOMING THE MEASUREMENT CHALLENGES OF ADVANCED SEMICONDUCTOR TECHNOLOGIES

# Introduction

# Meeting the measurement challenges of the 65nm node

For decades, IC performance gains have largely been due to shrinking device sizes. Today, given the challenges of sub-193nm lithography, gains beyond the 90nm node are increasingly driven by material and device innovations, rather than traditional scaling. Process development engineers must leave the comfortable, well-behaved world of the Si/SiO<sub>2</sub>/polysilicon/Al materials system and immerse themselves in the challenging world of SiGe-SOI/HfNO<sub>3</sub>/metal gate/low κ/Cu materials.

New materials demand new electrical measurements for process and device characterization. Time-to-market pressures force researchers to choose measurement equipment suppliers who also deliver measurement expertise and complete working solutions, including subsystems from supplier partners when necessary. Increasingly, chipmakers are choosing suppliers (like Keithley) willing to accompany them throughout the long journey from research and process development to process integration and volume production.

Keithley's capability for emerging measurement needs at the 65nm node and beyond includes:

- ullet Advanced high  $\kappa$  transistor gate measurements using RF C-V and charge pumping.

- Large quantities of on-wafer RF s-parameters at up to 40GHz for verifying process models.

- Isothermal DC and RF testing on SOI substrates.

- Characterizing new embedded memories like MRAM and PRAM.

- Reliability testing: NBTI, electromigration, TDDB, Cu via voiding.

- Femtoamp DC leakage on mobile ICs.

- Benchtop failure analysis.

OVERCOMING THE MEASUREMENT CHALLENGES

OF ADVANCED SEMICONDUCTOR TECHNOLOGIES

#### SECTION II

# Advanced Transistor Gates and Thin Oxides

# Integrating high frequency capacitance measurement for monitoring process variation of equivalent oxide thickness of ultra-thin gate dielectrics

#### Introduction

As CMOS transistors have gotten smaller and smaller, so has the thickness of their gate dielectrics. This presents a great challenge to traditional capacitance measurement used to monitor dielectric thickness for process variation. First, the relationship between the capacitance value in the inversion or accumulation region of the capacitance-voltage (C-V) curve to the gate oxide thickness is no longer simple. It's necessary to apply new models, including quantum mechanics and polysilicon depletion effects, to determine oxide thickness accurately from the C-V curve [1, 2]. Second, gate leakage increases exponentially as thickness decreases due to tunneling of carriers through the ultrathin gate [3]. The gate capacitor becomes very lossy due to high leakage, and the gate capacitance measurement shows roll-off effects in both the inversion and accumulation regions of the C-V curve [4]. These roll-off effects make it impossible for engineers to extract C<sub>ox</sub> directly and use it to monitor thickness variations in production. The roll-off behavior is also dependant on the DC leakage of the gate. Therefore, even for two gate dielectrics with the same physical thickness and area, the lower quality one with higher gate leakage will show the greater roll-off in the C-V curve, which makes it more difficult to monitor thickness variations.

Some roll-off effects in the C-V curve are device related [5, 6]. At high frequency, the two main factors are channel resistance and contact resistance. These effects could be modeled by a different equivalent circuit model and could be reduced by a new device layout. On the other hand, some of the roll-offs in C-V measurement are related to non-optimized setups, including cabling, connectors, and probe station setup [7]. The first part of the paper provides a comprehensive overview of difficulties and precautions on C-V measurement on ultra-thin gate dielectrics using LCR meters at high frequencies (1–100MHz). The second part of the paper explores C-V measurement at radio frequency (RF) as one of the approaches to solving the high leakage induced measurement problem. In general, the crossover to RFCV occurs for gate oxide equivalent oxide thickness (EOT) in the range of 1.7nm to 1.0nm.

### **Error analysis**

Most of the challenges of using the LCR meters currently available for monitoring EOT variation come from getting correct capacitance measurements on very leaky gate materials. The effect of gate leakage in capacitance measurement can be represented by the dissipation factor (D) or quality factor (Q), where

$$D = \frac{G}{\omega C}$$

, and

$$Q = \frac{1}{D}.$$

G and C are respectively the conductance and capacitance of the gate dielectrics, and  $\omega = 2\pi f$ , with f being the frequency of the AC stimulus. An ideal capacitor without any parasitics has an infinite Q or zero D, while an ideal resistor has an infinite D. As gate oxide thickness decreases to less than 2nm, the effect of higher D starts to show up in the capacitance measurement. It is not unusual to see gate capacitance have D larger than 10 or even 100 at 1MHz. The direct result of large D is a roll-off of the C-V curve in the inversion or accumulation region. Sometimes, the measured capacitance value is negative [8].

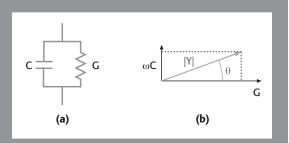

Let's quickly examine how measurement error is related to D. For the simple parallel circuit in **Figure 1a**, the capacitance error can be simplified as follows:

$$\frac{\Delta C}{C} = E_0 + \Delta \Theta \cdot D. \tag{1}$$

Here D can be expressed as

$$D + \frac{G}{\omega C} = \cot(\Theta) \tag{2}$$

and  $E_0$  denotes basic measurement error on a perfect capacitor. The definition of  $\theta$  (phase angle) is shown in **Figure 1b**.

Figure 1. Schematic diagram of equivalent circuit and AC impedance measurements:

- (a) Parallel equivalent circuit model

- (b) Definitions of phase and amplitude of AC impedance measurements.

**Eq. 1** is very important in determining errors in capacitance measurement at high D. First of all, it suggests that the measurement error is linearly dependent on D. In addition, it suggests that phase error, amplified by D, becomes the dominant source of error as D increases. There are two ways to reduce the capacitance measurement error: to increase the frequency, thereby reducing the D, or increase phase measurement accuracy, thereby reducing the phase error. Phase error comes from imperfections in the test system and measurement conditions, including cables and connectors, probes, and chuck.

### **High frequency C-V measurement with LCR meters**

It's not uncommon to question the minimum gate oxide thickness that current LCR meters can measure. In fact, what's important is not how thin the gate oxide is, but how leaky the gate is. As the quality of the gate oxide differs, material differs, and technology differs, gate oxides with similar equivalent oxide thicknesses may have leakage currents that differ by several orders of magnitude. One important factor to characterize the quality of the gate oxide, as described above, is D (dissipation factor) at a certain frequency (because D is inversely proportional to frequency). Since D is directly related to measured phase  $(\theta$ , as shown in **Eq. 2**), the principal limitation of currently available LCR meters is their inability to resolve small phase angles due to high dissipation factor. This is mainly because the test frequency is not high enough to reduce the D factor, and there is no calibration method on those LCR meters to measure the small phase angle accurately. This sets a theoretical limit on how well those LCR meters perform on thin gate oxide measurement. On the other hand, even when using a current LCR meter, the way in which the LCR meter is set up in the measurement system also affects the quality of the C-V measurement dramatically. We will briefly review some of the improvements that can be made when setting up an LCR meter, then assess the theoretical limitation of thin oxide measurement with existing LCR meters.

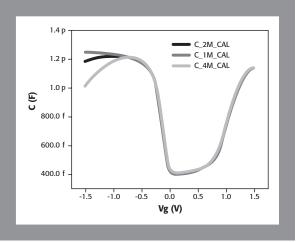

Cabling is very important in C-V measurements. The overall cable length in the system must be kept as close as possible to the calibration length of the LCR meter. Any deviation in physical cable length from the calibration cable length introduces phase error. **Figure 2** shows an example of the effects of different calibration cable lengths on C-V measurements on 1.3nm gate oxide. In the measurement setup, the physical cable length is close to two meters. Different cable length values are used as inputs for cable calibration and C-V curves are measured accordingly. In **Figure 2**, we see that capacitance measurements with small D (around 0V, since hardly any DC current flows at small DC bias) are not affected very much by variations in cable length; when D is small, the overall measurement error is dominated by E<sub>0</sub>, according to **Eq. 1**. Phase error does not play a leading role here. On the other hand, when D is large, such as in the inversion region, where large DC current flows due to tunneling, the cable-induced phase error effect becomes significant. When the calibration length is close to the actual physical

length, the inversion region is nice and flat. However, when the calibration length is shorter than the physical length, the curve starts rolling up. When the calibration length is longer than the physical length, the curve rolls off.

Figure 2. The effect of different cable calibration lengths on C-V measurement on a 1.3nm gate oxide transistor.

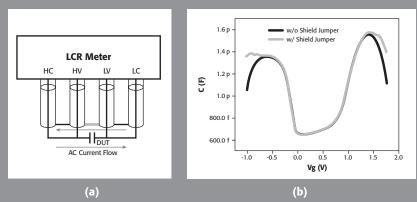

Proper shield jumper location is another factor in ensuring C-V measurement accuracy. Proper operation of an LCR meter requires that the shields of the coaxial cables be properly connected as close to the DUT as possible. These shields provide a current return path that compensates for parasitic inductance from the cabling (**Figure 3a**). If the cable shields are not tied properly, close to the DUT, there will be some parts of the cables (close to the contact point to the DUT) not returning current in the shield. This results in extra phase errors due to the inductance effect. **Figure 3b** shows the effect of proper shield connections on capacitance measurement, especially when D is high. As can be seen from **Figure 3b**, the measurement without the shield jumper shows large roll-offs in both the accumulation and inversion regions, while with the shield jumper close to the DUT, there is a significant reduction in roll-offs.

For C-V measurements in production environments, probe cards for ultra-thin oxide characterization are specially designed to reduce the parasitic capacitance and inductance of wiring and probe needles. To achieve the best results, we recommend using a special probe card with minimized parasitic capacitance reserved just for thin-gate C-V measurements. When measuring a four-terminal transistor, the source, drain, and substrate are tied together in the probe card level to achieve the shortest cables possible to those terminals. Shield jumpers, which as mentioned previously are critical to capacitance measurement on leaky capacitors, are used on the probe card so that the signal path shields are tied as close to the DUT as possible.

Figure 3. The effect of shield jumpers on C-V measurements:

(a) Correct cabling setup for C-V measurement. The gray line between the shields of the Voltage Force and Voltage Sense terminals (which are labeled HV and LV, respectively) is the shield jumper that ties the shields of the cables together close to the DUT.

(b) The effect of the shield jumper on the C-V measurement of a 1.3nm gate oxide. The C-V curve shows less roll-off in the inversion region with a properly located shield jumper.

Cable calibration is critical to successful C-V measurement on high D capacitors. Cable calibration includes open, short, and load calibrations. While both short and load calibrations require a proper test structure on the wafer (e.g., short and  $50\Omega$  load), open calibration does not. It has been found that the quality of short calibration determines the overall measurement quality. When calibrating on a short structure, there are inevitably some contact resistances. Short calibration with a high contact resistance results in noisy measurements and roll-offs in the C-V curve. Therefore, it is crucial to reduce contact resistance as much as possible during calibration. In a production environment, it is crucial to have an auto-calibration procedure. The system can be set up so that it performs calibration automatically when certain calibration criteria are met. Those criteria include the duration of the previous calibration, whether the previous calibration failed or not, or whether it is the first time to calibrate. To be consistent, calibration is only performed on the first wafer of every cassette. The user can change calibration criteria according to specific needs.

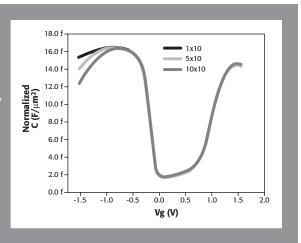

It is well known that some roll-offs in C-V curves are due to the channel resistance of the MOSFET [6]. **Figure 4** shows an example of capacitance measurements on three transistors with different gate lengths with area normalized capacitance value. Those transistors are on the same site on a wafer and very close to each other. It clearly shows that channel resistance-induced roll-off effect. Even though this effect can be compen-

Figure 4. The effect of channel resistance on C-V measurement on 1.3nm gate oxide. Three curves represent C-V measurements of 1µm×10µm, 5µm×10µm, and 10µm×10µm, and 10µm×10µm tansistors respectively. Measurement on shorter channel length shows less roll-off in the inversion region.

sated for by proper device modeling, it's undesirable in a production environment. We recommend using a short channel transistor to minimize channel resistance-induced roll-off. The trade-off of using a small area transistor is that the fringing capacitance is relatively large. Fortunately the fringing capacitance can be subtracted by measuring capacitances with two different gate areas. The area of the gate should be designed so that the capacitance value to be measured is around 1–2pF. Higher capacitance values result in measurement range overload due to high leakage, while lower capacitance values result in noisy measurements due to resolution limitations of the LCR meter.

Besides measurement accuracy, noise is another important factor with thin gate oxide C-V measurement. Again, based on **Eq. 1**, measurement noise is directly proportional to D factor. As D factor increases dramatically as gate thickness decreases, measurement noise, or repeatability of the measurement, which was not a problem before, becomes an issue. The most common source of noise is the chuck, especially a thermal chuck. If the device under test is not isolated from the chuck, as is typically the case with an NMOS transistor in a CMOS process, chuck noise can couple into measurement and becomes obvious when D is high. **Figure 5** shows the effect of measurement noise coupled with noise from a thermal chuck. There are several solutions to this problem:

- Use a better isolated, low noise chuck.

- Use higher frequencies so that D is reduced.

- Turn off the power to the thermal chuck when it's not in use.

- Design the test structure so that the chuck is isolated from the body of the transistor.

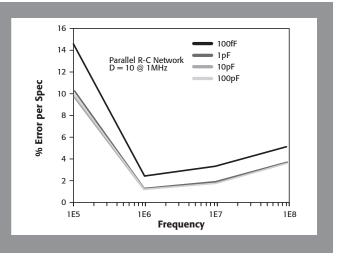

One common misunderstanding is that the higher the test frequency used, the better the capacitance measurement on thin gate oxide will be. In principle, this is true, because D is smaller at higher frequencies (this is usually true for frequencies less than 100MHz, where the DUT can be reprsented by a parallel equivalent circuit). However, to implement this principle with the LCR meters currently on the market, one other important factor must be considered, which is their basic measurement accuracy at higher frequencies. This is related to the  $E_0$  term in **Eq. 1**.  $E_0$  represents the measurement accuracy on an ideal capacitor (D = 0).  $E_0$  is a function of frequency. By reviewing the published specifications for currently available LCR meters [10], one can easily learn that the measurement accuracy degrades as frequency moves toward the high end of the frequency range (1–100MHz).

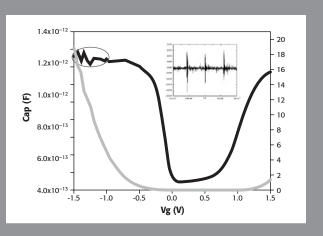

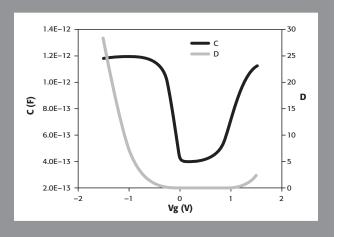

Another way to look at the problem is to combine dissipation factor, frequency, and the measurement specification for the LCR meter and draw a plot of measurement accuracy as a function of frequency. **Figure 6** shows that on a gate dielectric with a D=10 at 1MHz, the least error occurs at frequencies of around 1MHz. Therefore, a LCR meter with 1MHz capability should be sufficient for measuring gates with D=10. For example, as shown in **Figure 7** for a 1MHz C-V measurement on a 1.3nm oxide—the largest D at that frequency is close to 20.

Following a similar approach, if a gate dielectric has a D=100 at 1MHz, the sweet spot moves to a higher frequency (100MHz). However, at that frequency, the lowest measurement error rises to around 10%, which may be unacceptably high. To go even further, for a gate with a D=1000 at 1MHz, which is equivalent to D=10 at 100MHz, the minimum measurement error for frequencies up to 100MHz is around 30%, which

Figure 6.

Example of specification error of an LCR meter for D = 10 (1MHz) across frequency.

Figure 7. Example of C-V measurement at 1MHz on 1.3nm gate oxide.

makes this LCR meter completely unsuitable for this type of measurement. This exercise sets a theoretical limit on the maximum leakiness of an oxide that can be measured using the currently available LCR meters that operate at frequencies from 1 to 100MHz. Depending on the D of the material being measured, this exercise may be useful in determining the level of leakage at which a specific LCR can no longer measure a particular oxide. Alternatively, it's also possible, for a given D, to determine the optimal measurement frequency.

### RF capacitance measurement

With current LCR meters, the product of phase measurement accuracy and D, as in **Eq. 1**, is limited, which limits the capacitance measurement accuracy. At 110MHz, the infrastructure, including cabling, probe card, and calibration, is similar to that of an RF measurement. It requires a full calibration set, including phase, open, short, and load calibration. At the same time, performance is again limited by the product of phase measurement accuracy and D. With an alternative approach, using the RF technique, one can measure capacitance at much higher frequency, in particular at operating frequency, such as 2.4GHz. Usually the measurement is done at a frequency greater than 1GHz, the point of maximum Q. At such frequencies, D will remain relatively small for the foreseeable future (according to the International Technology Roadmap for Semiconductors) [11]. Conductance due to leakage ceases to be an issue.

The RF capacitance of the DUT is derived from the complex conductance (Y)

$$C = \frac{|Y|^2}{2\pi f \ Im(Y)} \,,$$

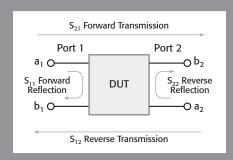

which is calculated from s-parameters measured on a two-port network (**Figure 8**). A vector network analyzer is used to measure the RF scattering parameters. The characteristic impedance of the overall transmission line of the system is optimized for  $50\Omega$ , with a 20GHz bandwidth. RF signals from the VNA are passed to the RF probe card through a dedicated pathway. The DC bias and RF signal are mixed in the Keithley S600 Series testhead in very close proximity to the DUT. The component of complex impedance (Z) of the DUT can be calculated from reflection parameters  $S_{11}$  and  $S_{22}$ ,

$$S_{11} = \frac{Z_{11} - Z_0}{Z_{11} + Z_0}$$

and  $S_{22} = \frac{Z_{22} - Z_0}{Z_{22} + Z_0}$

with  $Z_0 = 50\Omega$ . The frequency of measurement is selected so that the AC impedance of the DUT is close to  $50\Omega$ , because the measurement accuracy of the vector network

Figure 8. Schematic of a twoport network for s-parameter measurement.

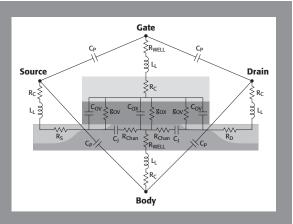

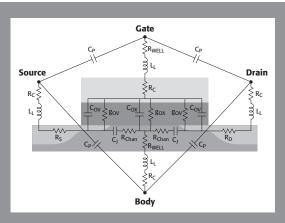

Figure 9. Simplified circuit model of a MOSFET including imperfections. The main factors to consider are parasitic capacitance between contact pads and leads (C<sub>P</sub>), contact resistance (R<sub>C</sub>), lead inductance (L<sub>L</sub>), channel resistance (R<sub>CH</sub>), and overlap capacitance (C<sub>OV</sub>). Most of the imperfection factors can be corrected by de-embedding.

analyzer is optimized around  $50\Omega$  impedance. For example, a 1pF capacitor has  $50\Omega$  impedance at around 3GHz.

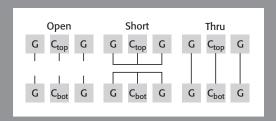

The parasitics embedded in the measurement system and the DUT are part of the technical difficulties involved in using RF measurement. Significant work has been done in measurement methodology and device layout to de-embed the parasitics. **Figure 9** shows a simplified circuit model of a real transistor. The goal of RF capacitance measurement is to get  $C_{\rm ox}$ . However,  $C_{\rm ox}$  is surrounded by imperfections in the physical device. Those imperfections include overlap capacitance between the gate contact and the source/drain well, gate resistance (due to poly silicon), lead inductance (from DUT to contact pads), contact resistance (between probe needle and contact pads), and channel resistance (mentioned previously). Some of the imperfections can be extracted by the de-embedding technique, especially the effects of contact resistance, lead inductance, and parasitic capacitance. DUT measurement results are corrected by subtracting those measured on de-embedding structures. Typical de-embedding structures include open, short, and thru (**Figure 10**). For short de-embedding,

$$Z = Z_{meas} - Z_{short}$$

,

for open de-embedding,

$$Y = Y_{meas} - Y_{open}$$

,

and for thru de-embedding,

$$\frac{1}{Y} = \frac{1}{Y_{meas}} - \frac{1}{Y_{through}}.$$

Combinations of two or more of the de-embeddings can also be used. It is common for open and short de-embeddings to be used together to correct both parasitic capacitance and contact resistance. Sometimes open and thru are used together when the series inductance of the DUT is not optimized.

One basic assumption of RF C-V measurement is that the characteristic impedance of the system's transmission line is  $50\Omega$ . The closer the impedance of the transmission line to  $50\Omega$ , the better the measurement result will be. The device layout on the wafer should be adjusted to match the transmission line impedance. A ground-signal-ground structure is required for RF measurement. As mentioned earlier, channel resistance effects will show up in C-V measurements on long-channel devices, especially at higher frequencies. It is recommended that small transistors be used for RF capacitance measurements. To achieve a better signal-to-noise ratio, many small area transistors can be connected in parallel to make a large device. More details on the design of test structures for RF C-V measurement are available [9].

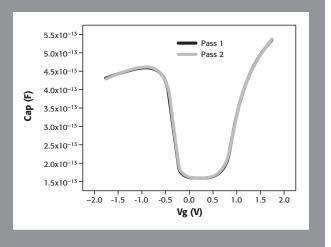

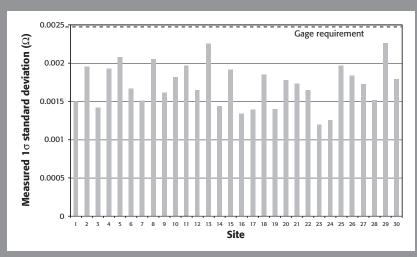

Contact resistance variations between consecutive probe contacts can limit the repeatability of RF C-V measurements. For example, if the DUT has a characteristic impedance of  $100 k\Omega$  at 1 MHz, a  $1 \Omega$  variation in contact resistance will cause only a 0.01% error. However, the characteristic impedance of the same device drops to  $100\Omega$  at 1 GHz, so that same  $1 \Omega$  variation in contact resistance will induce a 1% error. Most of the variation in contact resistance is due to buildup of aluminum oxide on the tip of the probe needle. These variations have been engineered out of the 8600 Series through the use of automated probe cleaning. A Gage R&R study shows less than 8000 variation in most cases (8000 variation in Gage R&R is considered "good"). **Figure 11** shows an example of repeated RF C-V measurements.

Calibrations down to the probe tips are required to make accurate measurements. A full calibration set includes open, short, thru, and load calibrations. Calibration will compensate for imperfections in the transmission line, including parasitic capacitance and lead inductance on the probe card and connectors. However, calibration cannot compensate for contact resistance, because the contact resistance between the probe

Figure 11. Overlay of two RF C-V measurements at 2.4GHz.

needle and the gold contacts on the calibration substrate is not the same as that between the probe needle and the aluminum pad on actual wafer under tests. These subtle differences are also compensated for in the \$600 Series automation.

A full suite of RF capacitance measurements involves:

- Loading calibration wafer and performing calibration. This is required only if the probe card is changed or if more than 72 hours has elapsed since the last calibration. The S600 Series accomplishes this in a way that is compliant with all 300mm automation requirements.

- Loading wafers from cassette.

- Performing s-parameter measurements on de-embedding structure (once per lot).

- Performing s-parameter measurements on actual DUT. The resolution of the Keithley system is sufficient to measure a single 100fF DUT, extract gate and fringing capacitance, and correct for poly depletion.

- Outputting de-embedded results.

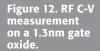

**Figure 12** demonstrates the correlation of RF C-V measurement results on a 13Å gate oxide at 2.4GHz with a 20MHz C-V measurement using an LCR meter. It shows excellent agreement between the two methods.

# **Comparison of high frequency and RF C-V techniques**

Comparing high frequency C-V (HFCV) and radio frequency C-V (RFCV) results only makes sense when both techniques can yield valid EOT measurements. In general, this applies to gate oxides with EOTs typically ranging from 1.7nm to 1.0nm. The actual range varies, depending on the specific process. For thick oxide, HFCV has a clear advantage because of cost and ease of use. For ultra-thin oxide, HFCV is no longer capable because of the reasons stated previously in this paper. When both HFCV and RFCV are valid options, the comparison shown in **Table 1** may help users determine the best time to migrate to RFCV based on cost, technology roadmap, and other factors.

Table 1.

| Factors               | Technique | Implementation                                             | Advantage                                                                      | Disadvantage                                                                      |

|-----------------------|-----------|------------------------------------------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| Device<br>layout      | HFCV      | DC                                                         | Compatible with existing DC parametric tests                                   | Cabling and connection<br>becomes harder at<br>higher frequency <sup>1</sup>      |

|                       | RFCV      | G-S-G, RF<br>De-embedding                                  | Parasitic extraction                                                           | Not compatible with DC parametric tests                                           |

| Device size           | HFCV      | Large                                                      | Less parasitic compared to gate capacitance                                    | Channel resistance<br>affects C-V<br>measurement                                  |

|                       | RFCV      | Small                                                      | Can measure short<br>channel devices,<br>reducing channel<br>resistance effect | Parasitic capacitance<br>has to be extracted<br>with de-embedding                 |

|                       |           |                                                            | Can measure working transistors, not test structures                           |                                                                                   |

| Contact<br>resistance | HFCV      | Dual frequency<br>C-V sweep                                |                                                                                | Requires two sweeps<br>Accuracy is limited by<br>instrument accuracy <sup>2</sup> |

|                       | RFCV      | De-embedding                                               | Only one frequency is needed                                                   |                                                                                   |

| Frequency             | HFCV      | 100kHz –<br>100MHz                                         |                                                                                |                                                                                   |

|                       | RFCV      | >100MHz                                                    | Measurement at operating frequency                                             |                                                                                   |

| DC current            | HFCV      | DC current flow into meter                                 |                                                                                | Measurement accuracy affected by DC current <sup>3</sup>                          |

|                       | RFCV      | DC current is<br>separated from<br>RF pathway <sup>4</sup> | RF measurement not affected by amount of DC current flow                       |                                                                                   |

#### Notes:

- At frequency >1MHz, special care has to be taken for cabling and connection (such as a dedicated signal pathway), an RF-like calibration suite, such as open, short, load, has to be deployed to calibrate down to the prober tip.

- 2. See [12].

- 3. See [8].

- 4. DC bias is provided by a source measure unit through a bias Tee, while RF measurement is AC coupled through the bias Tee using a Vector Network Analyzer.

#### Conclusion

Common C-V measurement errors with currently available LCR meters are discussed, as well as their limitations in making C-V measurements on ultra-thin gate oxides. Techniques to enhance an LCR meter's performance to near its theoretical limits, such as cabling, probe card, and connectors, are discussed. The RF C-V technique is discussed and deployed in production environment to monitor EOT variations for ultra-thin gate oxide. New options available make the S600 Series the ultimate tool for monitoring EOT variation in production environments for the current technology node, as well as for several future technology nodes.

#### References

- [1] N. Yang, W. K. Henson, J. R. Hauser, and J. J. Wortman, "Modeling Study of Ultrathin Gate Oxides Using Direct Tunneling Current and Capacitance-Voltage Measurements in MOS Devices," *IEEE Transactions on Electron Devices*, vol. 46, p. 1464, July 1999.

- [2] K.F. Schuegraf, et al., "Impact of Polysilicon Depletion in Thin Oxide MOS Technology," in Proc. VLSI-TSA, 1993, p. 86.

- [3] Y. Shi, T. P. Ma, S. Prasad, and S. Dhanda, "Polarity-dependent tunneling current and oxide breakdown in dual-gate CMOSFETs," *Electronics Device Lett.*, vol. 19, p. 391, Oct. 1998.

- [4] C. H. Choi, et al., "Capacitance reconstruction from measured C-V in high leakage, nitride/oxide MOS," *IEEE Transactions on Electron Devices*, vol. 47, p. 1843, Oct. 2000.

- [5] K. J. Yang and C.M. Hu, "MOS Capacitance Measurements for High-Leakage Thin Dielectrics," *IEEE Transactions on Electron Devices*, vol. 46, p. 1500, July 1999.

- [6] D. W. Barlage, et al., "Inversion MOS Capacitance Extraction for High-Leakage Dielectrics Using a Transmission Line Equivalent Circuit," *IEEE Electron Device Letters*, vol. 21, p. 454, Sept. 2000.

- [7] H. Suto, et al., "Methodology for Accurate C-V Measurement of Gate Insulators below 1.5nm EOT," in *Extended Abstract of the International Conf. On Solid State Devices and Materials*, 2002, p. 748.

- [8] Y. Okawa, H. Norimatsu, H. Suto, and M. Takayanagi, "The Negative Capacitance Effect on the C-V measurement of Ultra Thin Gate Dielectrics Induced by the Stray Capacitance of the Measurement System," in *Proc. ICMTS*, 2003, p. 197.

- [9] J. Schmitz, et al., "Test Structure Design Considerations for RF-CV Measurements on Leaky Dielectrics," in *Proc. ICMTS*, 2003, p. 181.

- [10] Agilent 4294 LCR meter specification, document #5968-3809E.

- [11] ITRS website: http://public.itrs.net/.

- [12] A. Nara, N. Yasuda, H. Satake, and A Toriumi, "Limitations of the Two-frequency Capacitance Measurement Technique Applied to Ultra-Thin SiO<sub>2</sub> Gate Oxides," in *Proc. ICMTS*, 2001, p. 53.

# Qualifying high K gate materials with charge-trapping measurements

### Hunting for high $\kappa$

As the size of transistors continues to scale down, the use of conventional SiO $_2$  as a gate dielectric material is approaching physical and electrical limits [1, 2]. The principal limitation is high leakage current due to quantum mechanical tunneling of carriers through the thin gate oxide [3]. To reduce gate leakage current, high dielectric constant (high  $\kappa$ ) gate materials, such as HfO $_2$ , ZrO $_2$  and Al $_2$ O $_3$  and their silicates [4], have drawn a great deal of attention in recent years. Due to their high dielectric constants, high  $\kappa$  gates can be made much thicker than SiO $_2$  while achieving the same gate capacitance. The result is lower leakage current—sometimes, several orders of magnitude lower.

One of the remaining challenges of deploying high  $\kappa$  materials is reliability. This includes phenomena affecting material reliability, such as voltage breakdown and defect generation mechanisms, and phenomena affecting device reliability, such as hot carrier injection. To characterize the reliability of high  $\kappa$  gate materials fully, multiple measurement techniques are typically required. Usually, these techniques include I-V, C-V, charge-pumping, and other measurements.

Various instruments can be used to take these measurements, but a fully integrated device characterization test system speeds up testing and provides a high level of data integrity. These systems typically integrate source-measure units with a C-V meter and pulse generator to characterize charge-trapping phenomena inside the high  $\kappa$  gate material. They can be used with various charge-trapping measurements, including a relatively new stress and charge-pumping technique that better characterizes traps in high  $\kappa$  films.

### Overview of charge-trapping measurement techniques

Charge-trapping techniques involve a series of voltage stresses of certain duration. During voltage stress, leakage current is measured in real time to calculate the amount of charge injected into the gate. This quantity is expressed as:

$$Q_{inj} = \int I_{Leakage}/dt$$

.

Between voltage stresses, three types of measurements can be done in sequence: C-V, I-V, and charge-pumping. From these measurements, important device parameters can be extracted and plotted as a function of time to show the degradation caused by the stresses.

Stress and C-V Measurements [5]. In this measurement, the device under test (DUT) usually is a MOS capacitor. A C-V sweep is performed on the DUT before and after voltage stress. The C-V sweep can be a full sweep from inversion to accumulation, so that a flat band voltage can be calculated by quantum mechanical modeling. However, a faster and easier way is to do the voltage sweep in a relatively small voltage range around an estimated flat band. The flat band voltage is then extracted from the C-V data. Either a single sweep or bi-directional sweep can be used; a bi-directional sweep will show any hysteresis effects. Flat band voltage as a function of stress time or injected charge provides information on how much charge is trapped in the gate stack structure. The trapped charge may be characterized by an effective value assumed to be located at the insulator-silicon interface ( $Q_{trap}$ ), given by:

$$Q_{trap} = C_{gate} \cdot \Delta C_{fb}$$

.

Trapped charge calculated from the change in flat band voltage is an approximation of the charge generated in the semiconductor-insulator interface. However, since charge can be generated in places other than this interface, stress and C-V measurements only give a rough estimate of how much is trapped due to injected charge. (See sample data in **Figure 1**.)

This measurement technique has the advantage of being simple and direct. It measures the effect of trapped charges from the C-V curve shift along the voltage axis as a function of injected charges. However, it is essential to avoid relaxation of trapped charges during the stress cycle. If trapped charges de-trap too fast, some of the trapped charges may be lost during switching between the stress and C-V measurements. Minimizing the switching time is the key to success in this measurement. Another drawback

Figure 1. A sample plot of trapped charges and flat band voltage shifts vs. injected charges for HfO<sub>2</sub> film with Equivalent Oxide Thickness = 1.2nm.

of this technique is that it measures the combination of traps initially in the film, plus those created later by the stress.

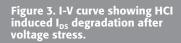

Stress and I-V measurement. Another method similar to the stress and C-V measurement is stress and I-V measurement on a MOSFET. During stress, the source, drain, and substrate terminals are grounded, so that stress is only applied on the gate dielectric. Then, after stress, a  $V_{\rm gs}$ - $I_{\rm d}$  test is performed, so that key parameters, such as threshold voltage and channel transconductance, are extracted. Plotting the shift of those parameters as a function of injected charge makes it possible to obtain the trapped charge density.

This method requires only I-V measurements, so it offers the advantage of being conducted without the need for a switching matrix. This can avoid or significantly reduce charge relaxation effects. However, modeling work is required to interpret the data.

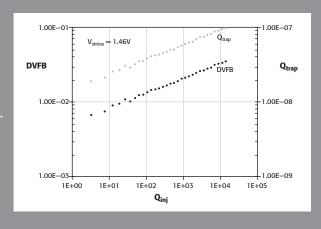

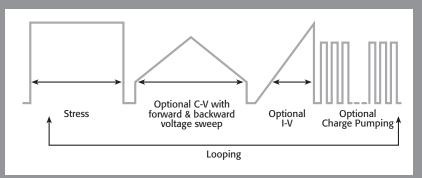

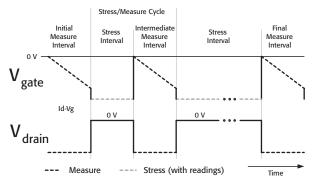

**Figure 2** is an example of voltage waveforms applied to an MIS capacitor in one stress cycle that includes stress, C-V, and I-V measurements. A forward and backward C-V sweep (center waveform in **Figure 2**) might be used to uncover any hysteresis effect in the high  $\kappa$  dielectric film. The instrumentation must be switched from stress to C-V measurement, so a voltage discontinuity appears at the DUT terminals during the switching time. This voltage discontinuity could result in relaxation of trapped charges from trapping centers. If so, the C-V measurement afterwards would indicate a smaller flat-band voltage shift due to fewer trapped charges. Therefore, the switching time between instruments must be minimized.

Charge-Pumping Measurement. Charge-pumping measurements are widely used to characterize interface state densities in MOSFET devices. This type of measurement is especially useful for thin gate materials that have relatively large gate leakage currents when accurate removal of the gate leakage is done [6, 7]. Such leakage makes it difficult, if not impossible, to collect simultaneous quasistatic and high frequency C-V measure-

Figure 2. Applied voltage waveform diagram for stress and C-V/I-V measurement.

ment data needed to estimate interface state densities. The interfacial-trapped charge (*Dit*) is calculated by:

$$D_{it} = \frac{I_{cp}}{qAf\Delta E} ,$$

where  $I_{cp}$  is the measured charge-pumping current, q is the fundamental electronic charge, A is the area, f is the frequency, and  $\Delta E$  is the difference between the inversion Fermi level and the accumulation Fermi level [8].

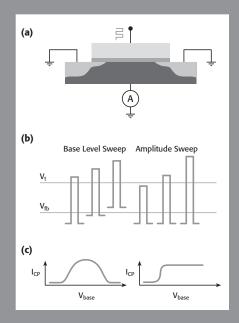

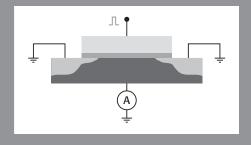

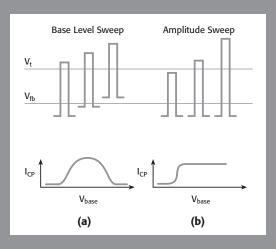

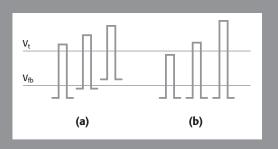

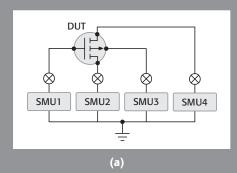

The basic charge-pumping technique involves the measurement of the substrate current while applying voltage pulses of fixed amplitude, rise time, fall time, and frequency to the gate of the transistor with the source, drain, and body tied to ground (**Figure 3a**). The application of the pulse can be done with a fixed amplitude voltage base sweep or with a fixed base variable amplitude sweep.

In a voltage base sweep, the amplitude and period (width) of the pulse are fixed while sweeping the pulse base voltage (**Figure 3b**). At each base voltage, body current can be measured and plotted against base voltage ( $I_{CP}$  vs.  $V_{base}$ ). The interface trap density ( $D_{ii}$ ) as a function of band bending can then be extracted from the charge-pumping current if the  $\Delta E$  is known.

Figure 3. Overview of chargepumping measurements:

- (a) Schematic for charge-pumping measurement; source and drain of the transistor are connected to ground; gate is pulsed with fixed frequency and amplitude while body current is measured.

- (b) Pulse waveform for base voltage sweep; pulse amplitude is constant.

- (c) Pulse waveform for amplitude sweep; base voltage is constant.

A fixed base, variable amplitude sweep has a fixed base voltage and pulse frequency with step changes in voltage amplitude (**Figure 3c**). The information obtained is similar to that extracted from a voltage base sweep, but in this case,  $I_{CP}$  vs.  $V_{peak}$  is plotted. These measurements can also be performed at different frequencies, so that a frequency response of interface traps can be obtained.

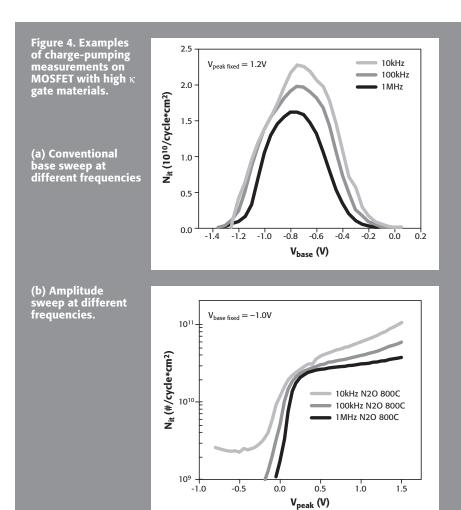

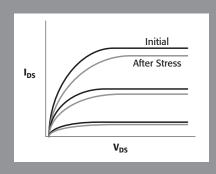

For high  $\kappa$  gate stack structures, the CP technique can quantify the trapped charge  $(N_n)$  as:

$$N_{it} = \frac{I_{cp}}{qfA,}$$

because trapped charge beyond the silicon substrate/interfacial layer can be sensed [9]. **Figure 4a** shows the characteristic  $N_{it}$  curve for the base voltage sweep technique, while **4b** shows the  $N_{it}$  characteristic for the fixed based, variable amplitude technique.

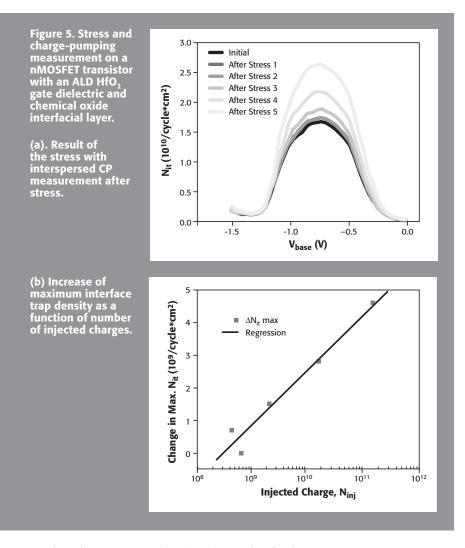

Stress and Charge-Pumping Measurement. Stress C-V, stress I-V, and charge pumping can provide information about charge centers associated with defects already in a gate dielectric film. However, for stress C-V and stress I-V, it isn't possible to distinguish between charge centers initially in the film and those created during a measurement stress cycle. Both types contribute to the shift in flat band voltage during measurements.

However, a recently developed technique can distinguish the initial charge-trapping centers from those created later in the film by voltage stresses. This technique uses a combination of stress and charge-pumping measurements. A major advantage of the new technique is that relaxation of trapped charges during the stress cycle will not affect overall measurement accuracy. The charge-pumping measurements detect traps in high  $\kappa$  gate stacks, so with some modeling work, it is possible to compare results of charge densities before and after a stress cycle. This indicates how many new charge centers were created by injected charges.

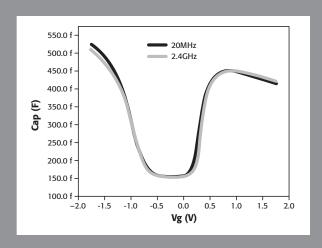

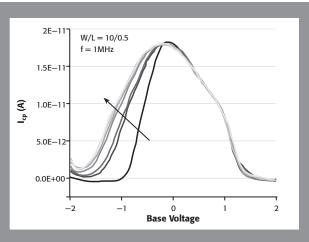

**Figure 5** shows results from stress charge-pumping measurements on a nMOSFET with W/L = 10/1mm. The gate stack is an ALD HfO<sub>2</sub> with a chemically grown interfacial oxide (EOT) of 1.7nm [10].

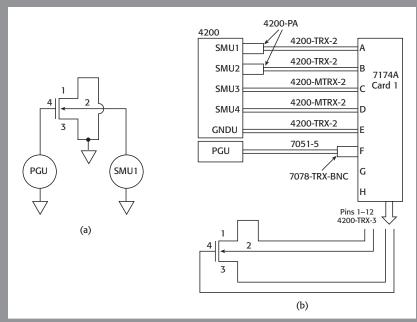

# **Test hardware arrangement**

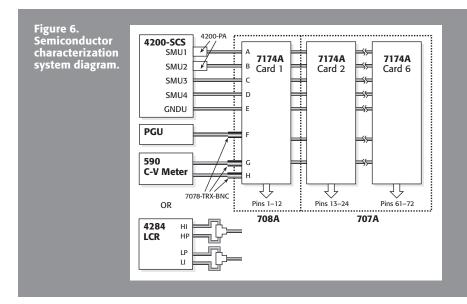

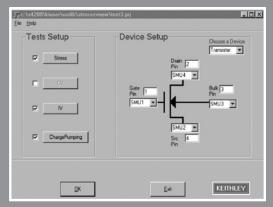

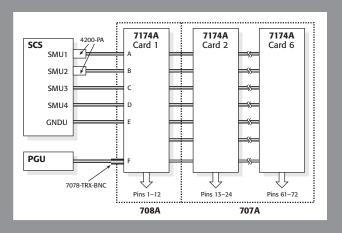

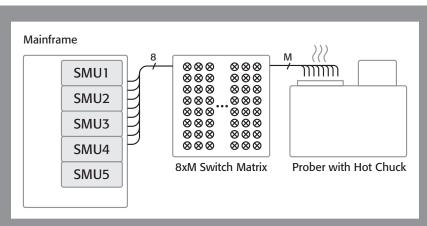

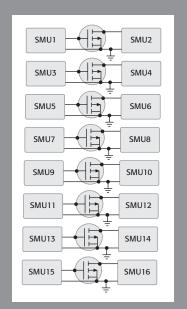

The core instrumentation for these measurements is a semiconductor characterization system (SCS) with multiple source-measure units (SMUs) and pre-amps that provide sub-femtoamp resolution for gate leakage currents. This instrumentation is combined with a capacitance measuring instrument, pulse generator, and semiconductor switching matrix for a complete measurement solution. An example of such a system appears in **Figure 6**. The equipment in this block diagram includes a:

• Keithley Model 4200-SCS Semiconductor Characterization System

- Keithley Model 590 C-V Meter or Agilent Model 4284 LCR Meter

- Agilent 8112 or 8110/81110 Pulse Generator Unit (PGU)

- Keithley Models 707A and 708A switching mainframes with Model 7174A ultra low leakage switch matrix cards

The pulse generator supplies the voltage pulses for charge-pumping measurements. The pulse generator and the C-V meter are connected to the rows of the switch matrix card. DUTs are connected to the columns of the matrix cards. The low leakage and minimal dielectric absorption of the 7174A cards ensure that DUT measurements can be made much faster and more accurately than with general purpose switching cards. The 4200-SCS also has dynamic Trigger Link outputs for control of internal and external in-

strumentation without using the GPIB, which also speeds up measurements. Its prober drivers provide manual and automatic control of on-wafer measurements.

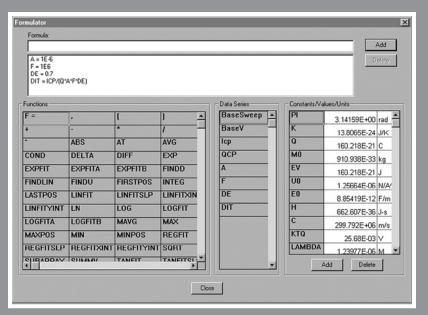

# System software and data communications

For this hardware, the test application is written for use with the Microsoft® Windows® operating system running on the PC in the SCS. The software provides test definition, automated control, parameter analysis, and data graphing. Built-in measurement configurations include a sweep mode with nine forcing functions, which reduces programming requirements. Communications between the CPU mainboard and SMUs takes place over a PCI interface, which is much faster than a GPIB interface. This is a key feature in minimizing switching time between stress, C-V, and I-V measurements.

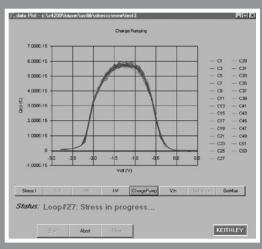

**Figure 7** shows two screen captures of the charge-trapping software interface for a test setup and a charge-pumping data plot. To get a complete picture of charge-trapping phenomena in high  $\kappa$  dielectric materials, it's necessary to configure individual tests for all the plausible combinations of stress, C-V, I-V, and charge-pumping measurements. Typical test variables are listed in **Table 1**. Depending on the SCS, data could be stored in text or Excel format for post-processing.

# **Acknowledgements**

The charge-trapping test application developed with the Keithley Model 4200-SCS was the result of a collaborative effort between Keithley, International SEMATECH

Figure 7. Charge-trapping software interface.

Table 1. List of tests and parameters extracted on charge-trapping test system

| Test Type                | Stress-Only                                    | Charge-Pumping<br>Only                                   | Stress - C-V/I-V                                                                                                              | Stress – Charge<br>Pumping                                         |

|--------------------------|------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| Measurement<br>Performed | Constant Voltage<br>Stress or Voltage-<br>Ramp | Base Voltage Sweep<br>Amplitude Sweep<br>Frequency Sweep | Dual C-V Sweep<br>V <sub>g</sub> -I <sub>d</sub> Test                                                                         | Stress and<br>Charge-pumping                                       |

| Parameters<br>Extracted  | TDDB or Q <sub>BD</sub> *                      | I <sub>cp</sub> , Q <sub>cp</sub> , D <sub>it</sub>      | Shift of V <sub>fb</sub> ,<br>V <sub>t</sub> , G <sub>m</sub> , sub-<br>threshold slope<br>as function of<br>injected charges | Charge Density,<br>new charge<br>created due to<br>injected charge |

<sup>\*</sup> TDDB—Time Dependent Dielectric Breakdown; Q<sub>BD</sub>—Charge to Breakdown.

(ISMT), and IMEC. Special thanks are extended to Kenneth Matthews of ISMT, Andreas Kerber and Eduard Cartier of IMEC, and Sufi Zafar of IBM for their contributions to this collaboration.

#### References

- [1] P. Packan, *Science* 285,2079 (1999).

- [2] D. Frank, R. Dennard, E. Nowak, P. Solomon, Y. Taur, and H.-S. Wong, *Proc. IEEE* 89, 259 (2001).

- [3]. S.-H. Lo, D. Buchanan, Y. Taur, and W. Wang, *IEEE Electron Device Lett.* 18,209 (1997).

- [4] E. Gusev, E. Cartier, D. Buchanan, M. Gribelyuk, M. Copel, H. Okorn-Schmidt, and C. D'Emic, *Proceedings of the Conference on Insulating Films on Semi*conductors, 2001.

- [5] S. Zafar, et. al., Applied Physics Letters, 81, 2608 (2002).

- [6] P. Masson, et al., "On the Tunneling Component of Charge Pumping Current in Ultrathin Gate Oxide MOSFETs," *IEEE Elect. Dev. Lett.*, Vol. 20, No. 2, pp. 92–94, 1999.

- [7] S.S. Chung, et al., "A Novel and Direct Determination of the Interface Traps in Sub-100nm CMOS Devices with Direct Tunneling Regime (12~16Å) Gate Oxide," 2002 VLSI Tech. Digest of Tech. Papers.

- [8] G. Groeseneken, H.E. Maes, N. Beltran, and R.F. De Keersmaecker, "A Reliable Approach to Charge-Pumping Measurements in MOS Transistors," *IEEE Trans. Electron. Dev.*, Vol. ED-31, pp. 42–53, 1984.

- [9] A. Kerber, E. Cartier, et al., "Origin of the Threshold Voltage Instability in SiO<sub>2</sub>/HfO<sub>2</sub> Dual Layer Gate Dielectrics," to be published in *IEEE Electron Device Lett*.

- [10] Y. Kim, A. Agarwal, R. Bergmann, et al., "Conventional n-channel MOSFET devices with polysilicon gate electrode using single layer HfO<sub>2</sub> and ZrO<sub>2</sub> as high κ gate dielectrics," *Technical Digest of the International Electron Device Meeting*, December 2–5, 2001, Washington, D.C., pp. 20.2.1–4.

# How to get accurate trap density measurements using charge pumping

The two most common methods used to characterize interface trap state densities in MOSFET devices are charge pumping (CP) and simultaneous C-V (the combination of high frequency and quasistatic C-V) measurement, which is typically done on MOS capacitors. As the size of the transistor scales down, thinner gate oxide is used to maintain proper gate control of the channel. This results in higher gate leakage current due to quantum tunneling of carriers through the thin gate. The higher gate leakage makes characterization of interface traps more and more difficult. Quasistatic C-V becomes impractical for oxide thicknesses less than 3—4nm. Even high frequency C-V measurement becomes a great challenge for oxides thinner than 2nm. The CP technique has much more tolerance than the quasistatic C-V technique, so it can be used for gate oxides thinner than 2nm, using special techniques to correct for excessive gate leakage [1].

After 40+ years of development, interface trap density in silicon dioxide gates is much less a concern than it was years ago, but SiO<sub>2</sub> as a gate dielectric material is approaching its physical and electrical limits [2]. The principal limitation is high leakage current due to quantum mechanical tunneling of carriers through the thin gate oxide [3]. Recently great attention has been paid to the use of high dielectric constant (high) materials, such as hafnium oxide (HfO<sub>2</sub>), zirconium oxide (ZrO<sub>2</sub>), alumina (Al<sub>2</sub>O<sub>3</sub>) and their silicates [4], as replacements for SiO<sub>2</sub> as gate dielectrics. Due to the high dielectric constants of these materials, high gates can be made much thicker than SiO<sub>2</sub> while maintaining the same gate capacitance. The result is lower leakage current—sometimes several orders of magnitude lower. Usually a very thin silicate layer forms between high film and Si substrate. The effect of this silicate layer on interface properties, as well as the charge trapping phenomena inside the high gate, is still to be understood. The CP technique becomes especially useful for characterizing interface and charge trapping phenomena, because the simultaneous C-V technique is very difficult (primarily due to the incapability of the quasistatic C-V technique at the high leakage level) for interface trap characterization.

This article will explain the basic CP technique and its variations and will describe some applications in characterizing charge trapping in high films.

# Test procedures and variations

The basic charge-pumping technique involves measuring the substrate current while applying voltage pulses of fixed amplitude, rise time, fall time, and frequency to the gate of the transistor, with the source, drain, and body tied to ground. **Figure 1** shows the

Figure 1. Schematic for charge pumping measurement; source and drain of the transistor are connected to ground; gate is pulsed with fixed frequency and amplitude while body current is measured.

Figure 2. Overview of charge pumping measurements: (a) Pulse waveform for base voltage sweep; pulse amplitude is constant. (b) Pulse waveform for amplitude sweep; base voltage is constant.

connections. The two most common ways to do charge-pumping measurements are a fixed amplitude, voltage base sweep (**Figure 2a**) or a fixed base, variable amplitude sweep (**Figure 2b**). For high gate stack structures, the CP technique can quantify the trapped charge ( $N_u$ ) as:

$$N_{it} = \frac{I_{cp}}{qfA}$$

(where  $I_{cp}$  is the measured charge-pumping current, q is the fundamental electronic charge, f is the frequency, and A is the area) since trapped charge beyond the silicon substrate/interfacial layer can be sensed [5].

In a voltage base sweep, the amplitude and period (width) of the pulse are fixed while sweeping the pulse base voltage. At each base voltage, body current can be meas-

Figure 3.

System setup

for charge

pumping

measurement

with a switch.

ured and plotted against base voltage. The interface trap density  $(D_{ii})$  can be extracted as a function of band-bending, based on this equation:

$$D_{it} = \frac{I_{cp}}{qAf\Delta E}$$

where  $\Delta E$  is the difference between the inversion Fermi level and the accumulation Fermi level [6].

A fixed base, variable amplitude sweep has a fixed base voltage and pulse frequency with step changes in voltage amplitude. The information obtained is similar to that extracted from a voltage base sweep. These measurements can also be performed at different frequencies to obtain a frequency response for the interface traps.

It's relatively easy to perform CP measurements and data analysis using a semiconductor characterization system (SCS) in combination with a pulse generator. **Figure 1** illustrates the connections for a device under test (DUT) with one SMU and a pulse generator without a switch matrix; in **Figure 3** a semiconductor switch matrix is included in the configuration.

## Effects of gate leakage

The measured current  $(I_m)$  is the result of averaging of CP current and gate leakage current, as shown in the following. We assume here that gate capacitance is very small, so we can ignore transient currents due to gate capacitance response to pulses. This ceases to be a good assumption if the gate area of transistor under test is relatively large.

$$I_m = I_{cb} + I_{leak}(peak) \cdot dutycycle + I_{leak}(base) \cdot (1 - dutycycle)$$

$I_{cp}$  decreases strongly as frequency decreases, but the averaged leakage current is not frequency dependent. By subtracting  $I_m$  at very low frequency, leakage current is taken out of the measured  $I_{cp}$ . **Figure 4a** shows  $N_{it}$  as a function of base voltage sweep at different frequencies. At lower frequency, because the leakage current is of the same order of the  $I_{cp}$ , the  $N_{it}$  curve is strongly offset. **Figure 4b** shows the corrected  $N_{it}$  by using current measured at 300Hz (not shown in the figure). The measurement was done on an n-MOSFET with a base sweep at frequencies from 3kHz to 1MHz with the amplitude of the gate pulse fixed at 1.2V.

Figure 5. 7+10 (a) Example of maximum N<sub>ir</sub> 6E+10 as a function of frequency. Because 5E+10 traps responding 4E+10 to high frequency pulses also respond Max. N<sub>it</sub> to low frequency pulses, maximum 3E+10 2E+00 N<sub>it</sub> at lower frequency is always 1E+10 larger than that at higher frequency. Maximum N<sub>it</sub> is 0E+00 extracted from 10kHz 100kHz 1kHz 1MHz Figure 3b. Frequency (b) Frequency distribution of measured interface 2.5E+10 traps. It is extracted by differentiating maximum N<sub>it</sub> with Oifferential N<sub>t</sub> (#/cm²) 2.0E+10 frequency from Figure 4a. 1.5E+10 1.0E+10 5.0E+09 0.0E + 001kHz 10kHz 100kHz 1MH<sub>7</sub> Frequency

# Frequency dependent trap density

CP measurements at different frequencies yield important information about interface trap density distribution across frequencies. This information is usually shown by plotting either the maximum of  $N_{tt}$  (cumulative) or the differential of the maximum value of  $N_{tt}$  as a function of frequency. **Figures 5a** and **5b** show cumulative and differential trap distribution across frequency respectively. Maximum  $N_{tt}$  was calculated from the  $N_{tt}$  curve in **Figure 4b** after leakage correction.

# **Initial Charge filling**

CP can be used to characterize initial stage of gate-channel interface. **Figure 6** shows CP measurement on a "fresh" (never been tested) MOSFET at 1MHz. A series of consecutive CP measurements was repeated. As shown on the graph, the shape of the  $I_{cp}$  curve changes as well as the magnitude at lower biases. It then saturates after a number of repeated measurements. This indicates formation of interface traps due to electrical stress imposed by the CP measurement.

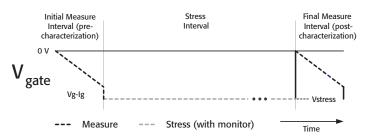

# Stress-CP measurement

CP measurement is useful alone. It can also be used together with DC or AC stress to study charge trapping as well as new charge creation on the high -Si interface, as well as inside the high film. Charges injected into high film due to stress are calculated by integrating gate current through stress time.  $Q_{inj} = \int I_{leakage} dt$ . The advantage of stress-CP measurement over traditional stress-C-V measurement (which measures the shift of flat band voltage due to stress) and stress-I-V (which measures the shift of threshold voltage due to stress) is that it can clearly distinguish existing charge trap centers with new centers created by stress [7]. Also, charge relaxation in CP measurement is usually much less than that in stress-C-V and stress-I-V measurements, where trapped charges will relax between stress and the next measurement.

# Conclusion

Charge pumping is a powerful tool for characterizing charging phenomena in high gate stacks. Its advantages include requiring less hardware, minimum software interface, relatively simple and easy to perform, good measurement accuracy on interface trap density, and good tolerance on gate leakage. It can characterize initial trap creation (on a fresh device) as well as new traps generated by injected charges (combining stress and CP).

# References

- [1] S.S. Chung, et al., "A Novel and Direct Determination of the Interface Traps in Sub-100nm CMOS Devices with Direct Tunneling Regime (12~16Å) Gate Oxide," 2002 VLSI Tech. Digest of Tech. Papers.

- [2] P. Packan, Science 285,2079 (1999).

- [3] S.-H. Lo, D. Buchanan, Y. Taur, and W. Wang, *IEEE Electron Device Lett.*, Vol. 18, p 209, 1997.

- [4] E. Gusev, E. Cartier, D. Buchanan, M. Gribelyuk, M. Copel, H. Okorn-Schmidt, and C. D'Emic, *Proceedings of the Conference on Insulating Films on Semi*conductors, 2001.

- [5] A. Kerber, E. Cartier, et al., IEEE Electron Device Lett. Vol. 24, pp 87-89, 2003.

- [6] G. Groeseneken, H.E. Maes, N. Beltran, and R.F. De Keersmaecker, *IEEE Trans. Electron Dev.*, Vol. ED-31, pp. 42-53, 1984.

- [7] Y. Zhao, C.D. Young and G.A. Brown, Semiconductor International, Oct, 2003.

OVERCOMING THE MEASUREMENT CHALLENGES

OF ADVANCED SEMICONDUCTOR TECHNOLOGIES

### **SECTION 3**

RF Modeling and Process Control of High Performance Analog and BiCMOS Devices

# RF wafer testing: an acute need, and now practical

# RF tests becoming indispensable

Leading semiconductor producers have recently conceded that wafer level RF measurements are acutely needed to develop and produce advanced ICs. To a certain degree, this flies in the face of the 2003 recommendations by the ITRS Technical Working Group for Modeling and Simulation, which states, "The parameter extraction for RF compact models preferably tries to minimize RF measurements. Parameters should be extracted from standard I-V and C-V measurements with supporting simulations, if needed." The problem is that standard I-V and C-V measurements make the direct extraction of  $C_{\rm OX}$  impossible for ultra-thin dielectrics due to high leakage currents and non-linearities. Yet, accurate parameter extraction for HF circuit modeling at 1–40GHz and for RF compact model verification has become essential. This challenge is increasing for high performance/low cost digital, RF, and analog/mixed-signal devices as the industry progresses toward the 65nm node and beyond.

The recommendations for minimizing the use of RF techniques are predicated on the assumption that they cannot be made effectively, particularly in a production environment, which may have been the case in the past. However, new parametric test systems now make fast, accurate, and repeatable RF parameter extraction almost as easy as DC testing. In fact, one system can take precise DC and RF measurements simultaneously, making it suitable for both lab and production use.

# RF testing apps

Whether you are manufacturing RFICs on III-V wafers for cell phone modules or high performance analog on silicon-based technology, predicting final product performance and reliability requires wafer level RF s-parameter measurements in development and production. These measurements are an important addition to DC data in forming a complete picture of device characteristics. They also offer significantly more information with fewer measurements than a DC-only test suite.

Power amplifier RFICs are an obvious candidate for high frequency testing. They are extremely complicated, yet susceptible to end market pricing pressures. This makes them highly sensitive to testing costs in production, where functional tests are conducted under low bias conditions from 1GHz up to 40GHz, depending on their design and application. RF measurements have been limited to functional tests of packaged parts at the end of the line, as this testing is perceived as high cost and problematical in terms of repeatable, accurate results.

IC fabricators can also use RF wafer level measurements to extract figure of merit parameters on various high performance analog circuits at the 180nm node and beyond. SOCs that combine memory with RF, analog, and high speed digital devices have comparable RF test requirements.

Characterizing equivalent oxide thickness (EOT) on high D gate dielectrics is critical in high performance logic devices at the 130nm node and beyond, in the development of new materials, and for continued scaling of future IC generations. For example, RF measurements can play an important role in accurate modeling of dielectrics and their behavior in MPU, ASIC, FPGA, and DSP devices. This has been done on prior generations of technology using multi-frequency capacitance measurements and with advancing technology there has been a shift to high frequency capacitance (HFCV) measurements. However, HFCV is inadequate for ultra-thin dielectrics, one reason being that the HFCV instrument (not the DUT) introduces a series resistance into the measurement.

# Challenges in standard I-V and C-V measurements

RF parameters extracted from s-parameter data are included in compact simulation models used by design engineers during product development. However, manufacturers have taken wafer level s-parameter data only in device modeling labs, due to the complex nature of the measurements and associated cost. Even in a lab environment, accurate extraction of RF parameters has been a challenge due to the sensitivity of the measurement to probe contact resistance variation. Making the large number of measurements required for production monitoring quickly has seemed impractical, if not impossible.

One of the main technical challenges in RF testing is accurate de-embedding of the DUT and measurement system. This is particularly true in the extraction of  $C_{\rm OX}$  when characterizing ultra-thin gate dielectrics. **Figure 1** is a simplified circuit model of a real transistor that shows the components which complicate direct measurement of  $C_{\rm OX}$ . These components include overlap capacitance between the gate contact and the source/drain well, gate resistance, lead inductance (from DUT to contact pads), contact resistance (between probe needle and contact pads), and channel resistance. These components must be segregated by the appropriate extraction after de-embedding. Correction algorithms are applied for contact resistance, lead inductance, and probe pad capacitance.

# Reluctance in adopting RF C-V

These difficulties have important implications in a production environment. Unreliable measurements can hinder yield management. A bad measurement result on a good device is referred to as alpha error. In a production environment, this may mean that a wafer has been improperly scrapped. The misleading ITRS information and the slow, painstaking process that many companies experience in their modeling labs combine

Figure 1. Simplified circuit model of a MOSFET DUT. The C<sub>OX</sub> measurement factors to consider are parasitic capacitance between contact pads and leads (C<sub>P</sub>), contact resistance (R<sub>C</sub>), lead inductance (L<sub>1</sub>), channel resistance (RChan), and overlap capacitance (C<sub>OV</sub>).

to make engineers reluctant to adopt production RF measurements, believing they will have high alpha error. It is also perceived that throughput and operational costs will be unacceptable and that a high level of technical support is required to interpret results. Low throughput on prior generations of RF systems resulted from calibrations and measurements needing to be repeated due to contact resistance problems. Calibrations on these older systems also did not hold for different measurement frequency sets. High operational costs are associated with manual probing of gold calibration standards, which have soft pads and expensive RF probes that wear out quickly with over-scrubbing. There is also the false perception in the market that a special prober or chuck is required for wafer level s-parameter measurements. These factors result in a high perceived cost of ownership for RF C-V and reluctance by users to adopt the solution.

Succinctly put, the industry's overall perspective on wafer level RF testing has been that it is complicated and expensive. This is based on a view of RF measurements as black art and that implementing them in a high volume fab, run by a production floor operator, is fantasy. Additional concerns regarding RF measurements in production are that:

- Extensive test structure changes are needed.

- Results are unstable, varying tool-to-tool, operator-to-operator, and day-to-day.

- RF specialists must baby-sit every tool.

- Substantially different lot routing and operational workflow may be required.

- It is doubtful this can be a real-time technique.

- Lab grade results are unlikely.

Nevertheless, by maintaining the status quo based on these perceptions, fabs are "flying blind" in the implementation of new designs and processes for RFICs, new gate materials, and other advanced devices. The consequences are design and process iterations that greatly increase costs and time to market, accompanied by lower initial yields.

### Third Generation Parametric Testers Provide a Solution

The key to making wafer level RF testing a production process control tool is fully automated measurements. This means that a robot delivers the wafer, the calibration standard, and the probe card to where they are needed. In other words, a major test system design goal is absolute data integrity without human intervention. If intervention is required, it should be accomplished by the fab host or the test controller, based on intermediate test results or operational requirements.

Third generation testers now available have features that allow this type of operation to 40GHz. Being designed specifically for a production environment, they avoid some of the attributes of testers designed for lab use. Lab instrument design focuses on optimizing the manual use-case and features other than those associated with production. However, users of these instruments pay for every extra gigahertz and other incremental features. There is no upgrade path to support changing needs from 6GHz to 65GHz as applications change. Third generation testers support this upgrade path.

Third generation testers address the need to automatically de-embed and extract the measurements according to the DUT characteristics, which is a major technical challenge in getting reliable  $C_{\rm ox}$  results. These algorithms, coupled with improved interconnect technology and automated calibration procedures, allow fast and accurate RF parameter extraction from s-parameter measurements.

Correcting random measurement artifacts is a prerequisite to accurate de-embedding. For example, any change in contact resistance in a system with  $50\Omega$  characteristic impedance limits repeatability. Instrumentation manufacturers must identify all the sources of instability in RF measurements and design the test system to avoid them. Innovative design of the system interconnections is required to provide repeatable links between major system components.

Automatically measuring probe contact resistance and adjusting probe overdrive is another way an instrument manufacturer can assure repeatable measurements. By measuring the actual value of the contact resistance before RF measurements are taken, they can be corrected for the value of contact resistance, especially important for pas-

sive devices. Another benefit of actually measuring contact resistance is the ability to automatically initiate probe tip cleaning when the resistance gets too high due to contamination. Good overdrive control and cleaning only when needed will increase probe life significantly, which reduces a major consumable cost. (RF probes cost about \$1000 each.) This should also be part of the statistical process control of the tester.

With stable and known parasitics, the Smith chart curves generated from collected data are free of artifacts; there is no need for specialists to analyze and interpret results. In older systems, an expert in RF measurements was required to monitor data (i.e. curve traces of every measurement set), look for strange or unexpected results, and then analyze those results to make sure they represented process variations, instead of measurement anomalies.

Improved logic in third generation parametric testers makes continuous monitoring of RF measurement quality a reality and reduces or eliminates the need for support by RF specialists. With these systems, different production floor operators can get repeatable real-time results across a wide range of products and production tools. RF measurements are almost as easy as making DC measurements, which are also required to completely characterize wafer devices. In fact, one third generation system can make DC and RF measurements simultaneously. (See sidebar.) This system contains a number of other refinements that speed up throughput, making it practical to do high volume wafer level testing for process monitoring and control. These same features speed up measurements in the modeling lab without sacrificing lab grade results, thereby shortening the development cycle and time to market. All this can be done without purchasing special probers, through easy system upgrades. When the calibration standard is stored on the prober, the operational work flow is identical to DC-only testing and is changed only during periodic maintenance cycles.

# **Innovative designs for RF testing**

For many years, RF parametric testing at the wafer level was the province of "big iron" ATE systems limited to 6GHz or less or lab systems that were not capable for production use. Both were impractical for statistical process characterization and monitoring. To solve these and other problems associated with existing systems, in 2001, Keithley introduced its DC/RF series of parametric testers.

With these systems DC and RF testing can be done in parallel, asynchronously. This means that DC tests can be run in the background as RF testing is performed or visa versa, depending on which type of testing has the more complex attributes. As soon as either set of measurements is complete, the system is ready to perform more tests. Empirical data shows that neither DC nor RF test results are affected by running all test types in parallel. Since DC and RF measurements can be made simultaneously with a single prober insertion, throughput is greatly increased. System software provides real-

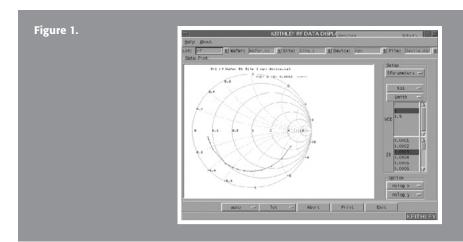

Figure 2.

time de-embedding and parameter extraction, while its mature point-and-click GUIs are unmatched by other systems in their ease of use.

The Keithley system design was influenced by a successful collaboration with several customers, resulting in innovations in interconnect and VNA integration, as well as adapting the parametric tester invented by Keithley to accommodate RF measurement needs. Since then there has been continuous improvement in all aspects of these systems, and in July 2003, Keithley received the Attendees Choice award at SEMICON-West for the 300mm production capability that was added.

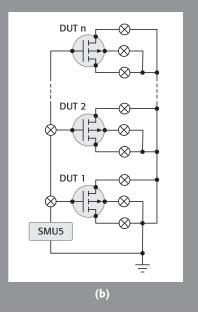

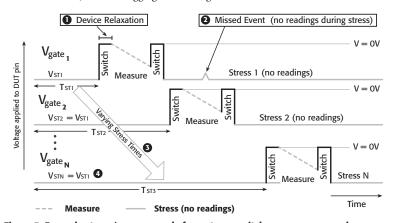

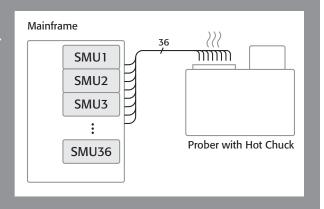

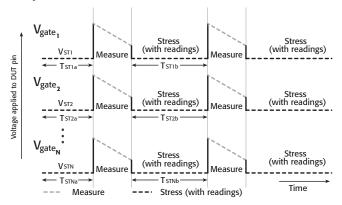

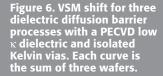

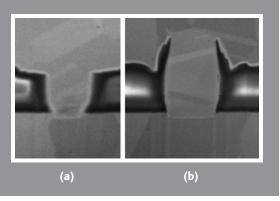

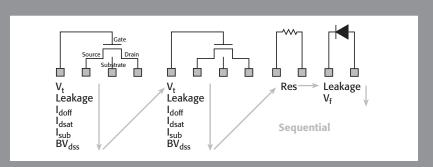

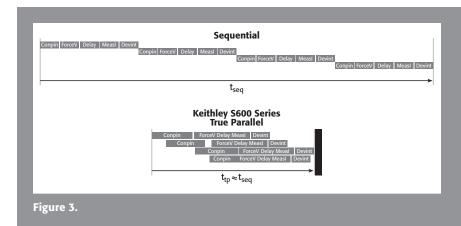

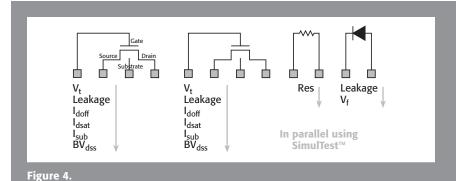

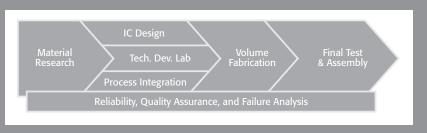

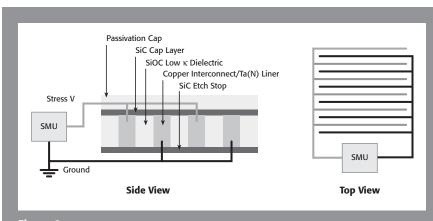

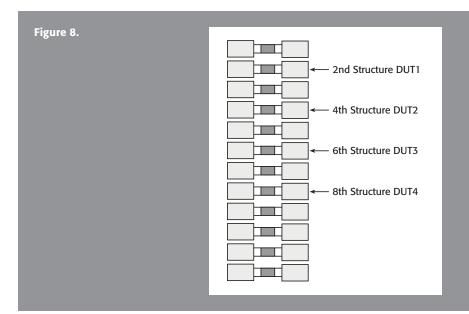

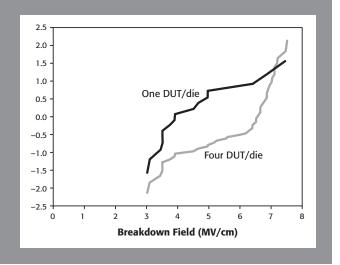

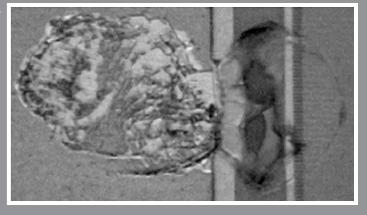

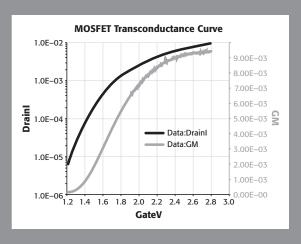

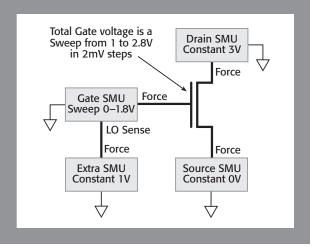

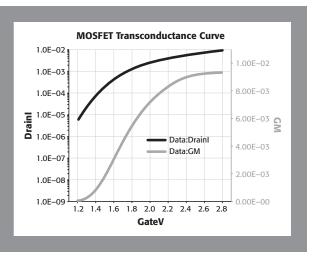

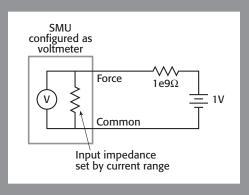

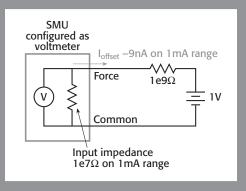

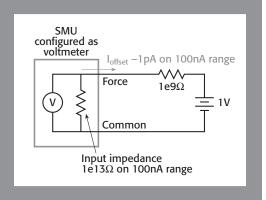

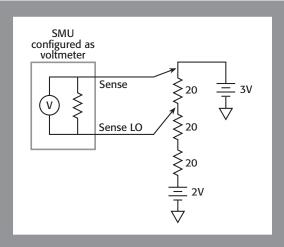

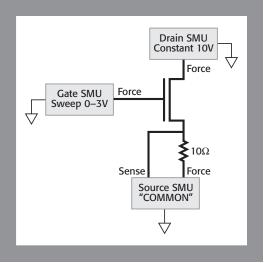

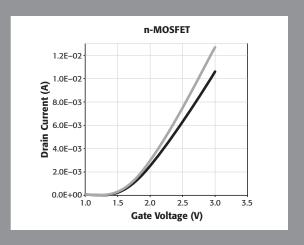

Recently, Keithley introduced the third generation of these DC/RF parametric testers (**Figure 2**) and already has several application successes with prominent semiconductor fabs. In these applications it was demonstrated that different technicians using the same system in a production facility could get the same results; in the past, this hasn't even been possible in the lab on other vendor's tools. When used in the lab, the Keithley tools provide excellent correlation with measurements made in production, even though the lab test suites are far more complex.